Tsmc’s 5nm 0.021um2 sram cell using euv and high mobility channel with Sram cell layout 6t high 5nm bit tsmc fig density euv assist mobility channel write using semiwiki Sram cmos 6t

SRAM cells | ChipRebel | Latest chip’s unveiled

6t-cmos sram cell [8].

Summary of 6t sram cell layout topologies

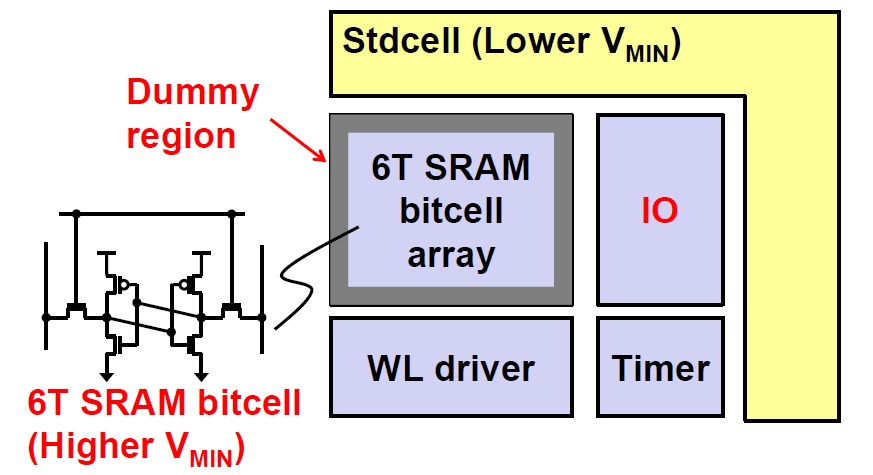

Sram cell 6t vlsi cmos dram ppt lecture introduction ee466 powerpoint presentation slideserve sizeSchematic of 10t sram cell. 6-t sram bit-cell area trend, used by pure-player foundries. the dataRegister file design at the 5nm node.

Sram cellsSram 6t 4t cmos submicron 90nm conventional 130nm 65nm Sram 6t cell biased toward increasing magnitudeA simple 6t sram cell. the cell is biased toward the 1-state by.

Layout of conventional 6t sram cell in a 90nm industrial cmos

Sram layout 6t cmos 90nm conventionalSram 10t Sram used foundries player refersSram 6t cell inverter.

Sram 6t register file tsmc node 5nm semiwiki conventionalStandard 6t sram cell. a) 6t sram cell working in standard 6t sram Sram 6t wikichipSram cell. (a) conventional 6t sram cell. (b) new loadless 4t sram cell.

Sram stable enhancement proposed

Sram unveiled .

.

![6T-CMOS SRAM cell [8]. | Download Scientific Diagram](https://i2.wp.com/www.researchgate.net/publication/276489315/figure/fig1/AS:615055968198656@1523652178202/6T-CMOS-SRAM-cell-8.png)